If other Caches have copy, they see BusRdX signal and Invalidate their copies.If other Caches have copy, they send value, otherwise fetch from Main Memory.State transition to (M) Modified in the requestor Cache.If other Caches have copy, one of them sends value, else fetch from Main Memory.State transition to (E) Exclusive, if none (must ensure all others have reported).State transition to (S) Shared, if other Caches have valid copy.other Caches see BusRd and check if they have a valid copy, inform sending cache.Table 1.1 State Transitions and response to various Processor Operations The State transitions and the responses at a particular state with respect to different inputs are shown in Table1.1 and Table 1.2 The snooping function on the memory side is done by the Memory controller.Įach Cache block has its own 4 state Finite State Machine (refer image 1.1).Snooper towards the Processor/Cache side.(Refer image above for MESI state diagram). The state of the block is changed according to the State Diagram of the protocol used. Every cache has a copy of the sharing status of every block of physical memory it has stored. Snooping Operation: In a snooping system, all caches on the bus monitor (or snoop) all the bus transactions. But in multicore architectures, where the coherence is maintained at the level of L2 caches, there is on chip 元 cache, it may be faster to fetch the missed block from the 元 cache rather than from another L2) ( Such Cache to Cache transfers can reduce the read miss latency if the latency to bring the block from the main memory is more than from Cache to Cache transfers, which is generally the case in bus based systems. FlushOpt: Snooped request that indicates that an entire cache block is posted on the bus in order to supply it to another processor(Cache to Cache transfers).Flush: Snooped request that indicates that an entire cache block is written back to the main memory by another processor.BusUpgr: Snooped request that indicates that there is a write request to a Cache block requested by another processor but that processor already has that Cache block residing in its own Cache.BusRdX: Snooped request that indicates there is a write request to a Cache block requested by another processor that doesn't already have the block.BusRd: Snooped request that indicates there is a read request to a Cache block requested by another processor.

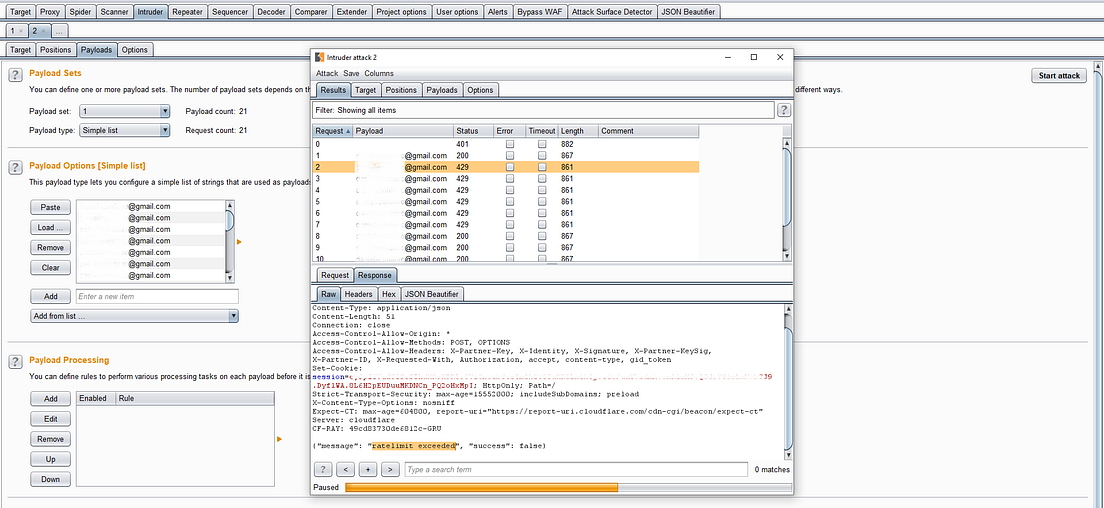

PrWr: The processor requests to write a Cache block.PrRd: The processor requests to read a Cache block.Processor Requests to Cache include the following operations: The bus requests are monitored with the help of Snoopers, which monitor all the bus transactions.įollowing are the different type of Processor requests and Bus side requests: The second stimulus comes from another processor, which doesn't have the Cache block or the updated data in its Cache, through the bus connecting the processors. For example: A processor P1 has a Block X in its Cache, and there is a request from the processor to read or write from that block. The first stimulus is the processor specific Read and Write request. The state of the FSM transitions from one state to another based on 2 stimuli. Image 1.1 State diagram for MESI protocol Red: Bus initiated transaction. When the block is marked M (modified) or E (exclusive), the copies of the block in other Caches are marked as I (Invalid). Invalid (I) Indicates that this cache line is invalid (unused).įor any given pair of caches, the permitted states of a given cache line are as follows: The line may be discarded (changed to the Invalid state) at any time. Shared (S) Indicates that this cache line may be stored in other caches of the machine and is clean - it matches the main memory. Alternatively, it may be changed to the Modified state when writing to it. It may be changed to the Shared state at any time, in response to a read request. Exclusive (E) The cache line is present only in the current cache, but is clean - it matches main memory. The write-back changes the line to the Shared state(S).

The cache is required to write the data back to main memory at some time in the future, before permitting any other read of the (no longer valid) main memory state. Modified (M) The cache line is present only in the current cache, and is dirty - it has been modified (M state) from the value in main memory. The letters in the acronym MESI represent four exclusive states that a cache line can be marked with (encoded using two additional bits):

0 kommentar(er)

0 kommentar(er)